# Chemical Stability and Electrical Performance of Dual-Active-Layered Zinc–Tin–Oxide/Indium–Gallium–Zinc–Oxide Thin-Film Transistors Using a Solution Process

Chul Ho Kim, You Seung Rim, and Hyun Jae Kim\*

School of Electrical and Electronic Engineering, Yonsei University, 50 Yonsei-ro, Seodaemun-gu, Seoul 120-749, Republic of Korea

**ABSTRACT:** We investigated the chemical stability and electrical properties of dual-active-layered zinc-tin-oxide (ZTO)/indium-gallium-zinc-oxide (IGZO) structures (DALZI) with the durability of the chemical damage. The IGZO film was easily corroded or removed by an etchant, but the DALZI film was effectively protected by the high chemical stability of ZTO. Furthermore, the electrical performance of the DALZI thin-film transistor (TFT) was improved by densification compared to the IGZO TFT owing to the passivation of the

pin holes or pore sites and the increase in the carrier concentration due to the effect of Sn<sup>4+</sup> doping.

**KEYWORDS:** thin-film transistors, dual-active-layered zinc-tin-oxide/indium-gallium-zinc-oxide, etch-stopper-layer, wet-etch, self-protection layer

## 1. INTRODUCTION

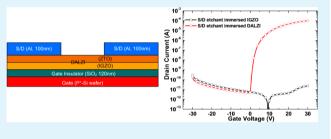

Recent studies on amorphous indium-gallium-zinc-oxides (a-IGZO) as channel materials have focused on their role as substitutes for conventional amorphous silicon (a-Si) or polysilicon for the backplanes of next-generation active-matrix organic light-emitting diode (AMOLED) displays and activematrix liquid-crystal displays (AMLCDs). The amorphous oxides have advantages such as high field-effect mobility, good uniformity, transparency in visible light, and compatibility with the conventional a-Si thin-film transistor (TFT) fabrication process. Moreover, the low-temperature deposition process of the IGZO thin film can be used to deposit channel materials on the bendable substrates used for flexible electronics.<sup>1-5</sup> In terms of fabrication process, IGZO thin film was easily damaged by its poor chemical stability under the metal etch process if the back-channel-etch (BCE) structure (Figure 1b) was employed. In order to protect the IGZO film surface from wet etch chemicals during the patterning of the source/drain (S/D) electrodes, it is essential to adopt the etchstopper-layer (ESL) structure (Figure 1a) instead of the BCE structure. When compared to the BCE structure, the ESL structure has demerits such as a high cost, an additional lithography process (equivalent to requiring an additional design mask), and the existence of a large parasitic capacitance caused by the misalignment margin among the gate, ESL, and S/D.<sup>6–11</sup> Therefore, new processes and novel IGZO TFTs with BCE structures have been studied to develop TFTs that offer low cost and better electrical performance.<sup>7</sup>

Zinc-tin-oxide (ZTO) is one of the promising oxidesemiconductor materials for the channel region in a TFT. Even though ZTO has higher chemical stability than IGZO owing to its  $SnO_2$  content, it is not widely used in the display industry compared to IGZO, which has high mobility and high

reliability. In this study, we demonstrated fabrication of a simple BCE-based, chemically durable, dual-active-layered ZTO/IGZO (DALZI) TFT using a solution process. We devised the dual-active-layered structure using the IGZO thinfilm as the front-channel and the ZTO thinfilm as the back-channel. The IGZO front channel played the role of the main electron accumulation layer, while the ZTO thinfilm served as a protection layer to shield the IGZO thin film from conventional wet etchants used to form the S/D patterns. Furthermore, the ZTO thin film provides the contact resistance with the S/D electrodes for the switching device because it has the characteristics of a neutral degenerate semiconductor, compared with the high contact resistance of the ESL which has mainly an insulator property.<sup>7,9,10</sup> As a result, a DALZI TFT exposed to a wet etchant could show superior TFT performance without an ESL.

## 2. EXPERIMENTAL PROCEDURE

**2.1. Preparation of IGZO and ZTO Solutions.** A 0.1 M IGZO solution was synthesized by dissolving indium nitrate hydrate  $[In(NO_3)_3:xH_2O]$ , gallium nitrate hydrate  $[Ga(NO_3)_3:xH_2O]$ , and zinc nitrate hydrate  $[Zn(NO_3)_2:xH_2O]$  in 2-methoxyethanol as a solvent, with acetic acid as a stabilizer. The molar ratio of In:Ga:Zn was fixed at 3:1:2. After the IGZO solution was stirred for 1 h at 70 °C to form a homogeneous solution, it was passed through a 0.2  $\mu$ m syringe filter and aged for over 24 h. A 0.15 M ZTO solution with a Zn:Sn molar ratio of 2:1 was prepared by dissolving zinc acetate dehydrate  $[Zn(Ac)_2:2H_2O]$  and tin(II) chloride  $[SnCl_2]$  in 2-methoxyethanol. The stirring and filtering of the ZTO solution were performed under the same conditions as for the IGZO solution.

Received:

March 15, 2013

Accepted:

June 5, 2013

Published:

June 5, 2013

Figure 1. Schematic cross-section of the (a) ESL-structured IGZO TFT, (b) BCE-structured a-Si TFT, and the simple unpassivated BCE-structured (c) IGZO TFT and (d) DALZI TFT.

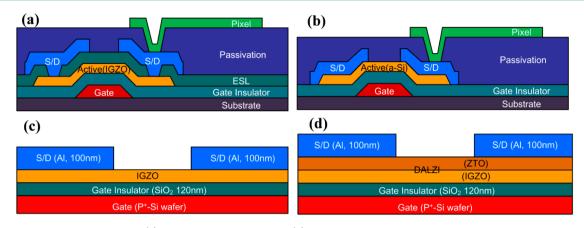

Figure 2. Optical microscopy image in plane view of (a) the immersed IGZO thin film and (b) the immersed ZTO thin film. (c) Transfer characteristic curves of the IGZO TFT as functions of the immersion process.

**2.2. Device Fabrications.** Schematics of the simple unpassivated BCE-structured IGZO TFT and DALZI TFT are shown in Figure 1c and d. For the fabrication of the IGZO TFT, an IGZO solution was spin-coated on a SiO<sub>2</sub> layer with a thickness of 120 nm (as the gate insulator), which was thermally grown on a heavily boron-doped Si wafer (as the gate electrode). The spin-coated thin film was prebaked at 300 °C in the air for 5 min to remove the solvent; it was then annealed at 450 °C in the air for 4 h. The as-annealed IGZO film had a thickness of about 10 nm. For the fabrication of the DALZI TFT, the ZTO thin film was formed with a thickness of about 20 nm on the IGZO thin film. Each layer of the DALZI TFT was annealed for 2 h, and the total annealing time was the same compared to the IGZO TFT.

To investigate the chemical durability of the IGZO thin film and the DALZI thin-film stack, we immersed the IGZO TFTs and the DALZI TFTs in an aluminum etchant (AL-11 with 72% phosphoric acid, 3% acetic acid, 3% nitric acid, and 22% water, Cyantek Co.) for 60 s at 50 °C. The etchant is used as a conventional etchant for patterning

aluminum as S/D electrodes. Finally, aluminum S/D electrodes with a thickness of 100 nm were deposited on the S/D-etchant-immersed IGZO and DALZI structures via sputtering with a shadow mask. The channel area was defined with a channel width (W) of 1000  $\mu$ m and a length (L) of 150  $\mu$ m. The microstructural properties of the IGZO thin film and DALZI thin-film stack were analyzed via transmission electron microscopy (TEM) and optical microscopy (OM). The electrical properties of the films and TFTs were analyzed via Hall-effect measurements and the use of a semiconductor parameter analyzer in the dark at room temperature, respectively.

## 3. RESULTS AND DISCUSSION

**3.1. The Chemical Stability of the IGZO and ZTO Layer.** The IGZO thin film with the photoresist (PR) pattern was immersed in an aluminum etchant for 60 s at 50 °C. Figure 2a shows the OM image of the IGZO film surface after the PR pattern was removed. The immersed IGZO thin film provided

#### **ACS Applied Materials & Interfaces**

an alternative way to study the effect of an aluminum etchant on IGZO as an exposed channel layer in the BCE structure during S/D patterning. Besides, 60 s is the time specified to etch the 900-nm-thick aluminum S/D and would be sufficient to etch the S/D used in conventional flat panel displays. Striped patterns of the IGZO thin film were formed owing to the poor chemical stability in an aluminum etchant, as shown in Figure 2a. However, the ZTO thin film was not changed by the aluminum etchant, as shown in Figure 2b, owing to the high chemical stability of SnO<sub>2</sub>.<sup>12</sup> This result indicated that the ZTO layer could protect the IGZO layer from the conventional wet etchants used in S/D patterning. Figure 2c shows the transfer characteristic curves of the IGZO TFT as functions of aluminum etchant exposure before S/D deposition at a drainto-source voltage  $(V_{DS})$  of 10.1 V. The nonimmersed IGZO TFT showed normal switching behavior. However, the immersed IGZO TFT showed the only leakage current regardless of gate voltage value. This result suggested that the IGZO channel layer was fully etched by the aluminum etchant, and the IGZO TFT lost the switching capabilities.

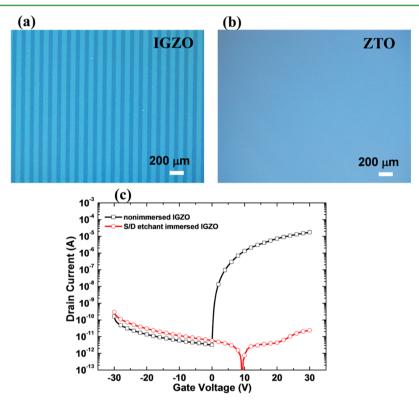

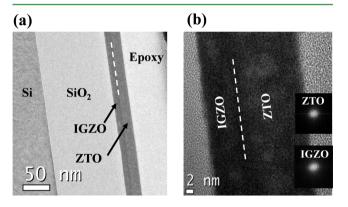

**3.2. Analysis on the Structure of DALZI Layer.** Figure 3a shows the cross-sectional TEM image of the DALZI

**Figure 3.** (a) Cross-sectional TEM image and (b) magnified highresolution TEM image of the immersed DALZI thin-film stack. (Inset) SAED patterns of the IGZO and the ZTO thin film.

structure after it was immersed in an aluminum etchant for 60 s; a magnified high-resolution TEM image is shown in Figure 3b. No aggregation or defects at the interface between the IGZO and ZTO thin films were observed in the ZTO/IGZO stack on SiO<sub>2</sub>, which suggested that the IGZO layer was protected by the ZTO layer despite the immersion process. In addition, the crystallinity of the IGZO and ZTO thin films was examined using selected area electron diffraction (SAED) patterns, as shown in the inset of Figure 3b. We could confirm that both IGZO and ZTO thin films were in the amorphous phase based on the broad, diffuse diffraction rings.

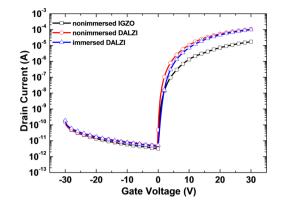

**3.3. Electrical Characteristics of DALZI TFTs.** Figure 4 shows the transfer characteristic curves of the IGZO- and DALZI-based TFTs under different immersion conditions before S/D deposition at a  $V_{DS}$  of 10.1 V. The nonimmersed DALZI TFT and the immersed DALZI TFT showed field-effect mobilities ( $\mu_{FE}$ ) of 2.09 and 1.97 cm<sup>2</sup>/V·s, threshold voltages ( $V_{TH}$ ) of 2.72 and 3.94 V, and subthreshold swings (SS) of 0.49 and 0.58 V/decade, respectively (as listed in Table 1). The DALZI TFT retained its switching properties regardless of the immersion process compared to the IGZO TFT, indicating that the ZTO layer provided good protection from damage by the aluminum etchant. When comparing the

**Figure 4.** Transfer characteristic curves of the IGZO and DALZI TFTs as functions of the immersion process.

Table 1. Comparison of Device Parameters of the IGZO and DALZI TFTs as a Function of the Immersion Process

| device structure  | $\mu_{\rm FE}~({ m cm}^2/({ m V~s}))$ | $V_{\rm TH}$ (V) | SS (V/decade) |

|-------------------|---------------------------------------|------------------|---------------|

| nonimmersed IGZO  | 0.32                                  | 4.43             | 0.55          |

| immersed IGZO     |                                       | no active        |               |

| nonimmersed DALZI | 2.09                                  | 2.72             | 0.49          |

| immersed DALZI    | 1.97                                  | 3.94             | 0.58          |

characteristics of the nonimmersed IGZO TFT and the immersed DALZI TFT (Table 1), the immersed DALZI TFT showed even better electrical performances.

We assumed two probabilities of the improved device characteristics. The first could be attributed to passivation of the porous IGZO thin film, including the large numbers of pin holes and pore sites. Solution-processed oxide films usually have low density and high porosity. However, stacking the ZTO thin film on top of the IGZO thin film could passivate the pin holes or pore sites as a result of the penetration of Zn and Sn atoms in the liquid phase.<sup>15,16</sup> In the second, the improved characteristics could be attributed to the doping behavior of  $Sn^{4+}$  ions that replaced the  $In^{3+}$ ,  $Ga^{3+}$ , or  $Zn^{2+}$  ions in the IGZO thin film, which could determine the overall DALZI TFT performance due to its location directly adjacent to the TFT gate dielectric, during annealing of the spin-coated DALZI stack. In other words, the Sn<sup>4+</sup> ions acted as cationic dopants in the IGZO lattice and served as substitutes for indium, gallium, or zinc. In In<sub>2</sub>O<sub>3</sub>, Ga<sub>2</sub>O<sub>3</sub>, and ZnO, since the metal ions had valences of two and three, the Sn ions acted as *n*-dopants of the IGZO lattice by providing electrons to the conduction band.<sup>26-30</sup> Therefore, the electrical conductivity of the DALZI structure was increased, supported by the larger carrier concentration  $(1.34 \times 10^{16} \text{ cm}^{-3})$  of the immersed DALZI thin-film stack compared to that (1.47  $\times$   $10^{15}~{\rm cm}^{-3})$  of the nonimmersed IGZO thin film obtained through hall measurements. We found slight degradation of the immersed DALZI TFT compared to the nonimmersed DALZI TFT. The carrier concentration of the nonimmersed DALZI thinfilm was also measured as  $1.46 \times 10^{16}$  cm<sup>-3</sup>. This result indicates that the immersed DALZI layer was slightly damaged rather than perfectly immune by the aluminum etchant.

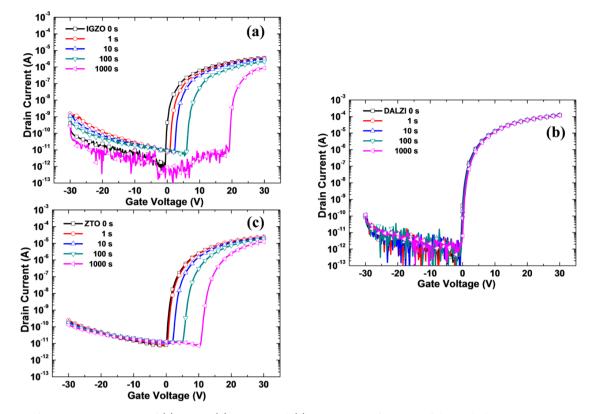

**3.4. Bias Stability of DALZI TFTs.** To investigate the effect of the ZTO thin film serving as a protection layer on the bias stability of the DALZI TFTs in terms of the instability of the oxide semiconductor TFT,<sup>23-25</sup> the positive bias stress (PBS) was performed at a  $V_{\rm GS}$  = 20 V and a  $V_{\rm DS}$  = 10.1 V. The maximum stress duration was 1000 s. Unpassivated IGZO

Figure 5. Transfer characteristic curves of (a) IGZO, (b) DALZI, and (c) ZTO TFT as functions of the applied stress time.

TFTs with the same active layer thickness of DALZI were fabricated using a 0.3 M IGZO solution considering the effect of active layer thickness on the bias stability.<sup>17–19</sup> Figure 5a and b show the transfer curves as a function of the applied stress time for the unpassivated IGZO TFT and DALZI TFT, respectively. The positive shift in  $V_{\rm TH}$  without significant change in  $\mu_{\rm FE}$  was founded. The unpassivated IGZO TFT showed a large  $V_{\text{TH}}$  shift of 19.2 V (from 0.5 to 19.7 V), while a  $V_{\rm TH}$  shift of the DALZI TFT was very small at 0.6 V. The superior stability of the DALZI TFT could be attributed to not only the reduction of trap sites by the passivation of the porous IGZO thin film due to the stacked-ZTO but also the middleinterface formed by the stacked-DALZI structure between the IGZO and ZTO layer. Previous papers have reported that the middle-interface capturing free electron contributed to weakening of the electric filed under gate voltage stress.<sup>15,21,33</sup> Therefore, the DALZI TFT has good stability under the PBS due to the decrease in the interaction between the exposed back surface and oxygen in ambient atmosphere, as well as the reduction of trap sites.<sup>22</sup> The PBS stability of the unpassivated single layer ZTO (0.15 M) TFT for confirming the effect of the upper layer ZTO on the stability of the DALZI TFT is shown in Figure 5c. The stress condition is the same as that of the IGZO and DALZI TFT. The positive shift in  $V_{\rm TH}$  of the ZTO TFT was smaller than that of the IGZO TFT but much larger than the DALZI. This result indicates that the improved stability of the DALZI TFT was not caused by the ZTO layer alone but by the advantage of the stacking process in the solution process.

#### 4. CONCLUSION

In summary, we investigated the chemical stability and electrical properties of IGZO and DALZI films and TFTs with the simple unpassivated BCE structure instead of the ESL structure. We found that the ZTO layer in the DALZI structure offered many advantages, including the following properties: (1) protection of the IGZO channel layer from an aluminum S/ D etchant, (2) densification of the IGZO channel layer owing to the passivation of the pin holes or the pore sites, (3) an increase in the carrier concentration owing to the doping behavior of Sn<sup>4+</sup>, and (4) support of the superior stability under the PBS due to the densification of the IGZO channel. Although the active patterning of DALZI could be considered to have difficulty due to the low sensitivity of wet etching of the ZTO layer, this problem could be resolved by using a common etchant of IGZO and ZTO such as oxalic acid.  $^{31,3\check{2}}$  Therefore. the DALZI structure with the self-protection layer of the chemical damage would ultimately lead to high-performance oxide TFTs with BCE structures.

## AUTHOR INFORMATION

#### Corresponding Author

\*E-mail: hjk3@yonsei.ac.kr.

## **Author Contributions**

C.H.K. and Y.S.R. contributed equally to this work.

#### Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

This work was supported by Samsung Display and the National Research Foundation of Korea (NRF) grant funded by the Korean Ministry of Education, Science and Technology (MEST) [no. 2011-0028819].

## **ACS Applied Materials & Interfaces**

## REFERENCES

- (1) Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. *Nature* **2004**, 432, 488–491.

- (2) Fortunato, E.; Barquinha, P.; Martins, R. Adv. Mater. 2012, 24, 2945–2986.

- (3) Park, J. S.; Maeng, W. J.; Kim, H. S.; Park, J. S. Thin Solid Films **2012**, 520, 1679–1693.

- (4) Lim, W.; Jang, J. H.; Kim, S. H.; Norton, D. P.; Craciun, V.; Pearton, S. J.; Ren, F.; Shen, H. Appl. Phys. Lett. 2008, 93, 082102.

- (5) Kamiya, T.; Nomura, K.; Hosono, H. Sci. Technol. Adv. Mater. 2010, 11, 044305.

- (6) Kwon, J. Y.; Lee, D. J.; Kim, K. B. Electron Mater. Lett. 2011, 7, 1–11.

- (7) Xu, H.; Lan, L.; Xu, M.; Zou, J.; Wang, L.; Wang, D.; Peng. J. Appl. Phys. Lett. **2011**, 99, 253501.

- (8) Lee, S. H.; Seo, B. H.; Seo, J. H. J. Korean Phys. Soc. 2008, 53, 2603–2606.

- (9) Ryu, S. H.; Park, Y. C.; Mativenga, M.; Kang, D. H.; Jang, J. Electrochem. Solid State Lett. 2012, 1, 17–19.

(10) Mativenga, M.; Choi, J. W.; Hur, J. H.; Kim, H. J.; Jang, J. J. Inf. Display **2011**, *12*, 47–50.

- (11) Kim, M.; Jeong, J. H.; Lee, H. J.; Ahn, T. K.; Shin, H. S.; Park, J. S.; Jeong, J. K.; Mo, Y. G.; Kim, H. D. *Appl. Phys. Lett.* **2007**, *90*, 212114.

- (12) Jayaraj, M. K.; Saji, K. J.; Nomura, K.; Kamiya, T.; Hosono, H. J. *Vac. Sci. Technol. B* **2008**, *26*, 495–501.

- (13) Tamai, T.; Ichinose, N.; Kawanishi, S.; Nishii, M.; Sasuga, T.; Hashida, I.; Mizuno, K. *Chem. Mater.* **1997**, *9*, 2674–2675.

- (14) Bradshaw, G.; Hughes, A. J. *Thin Solid Films* **1976**, 33, L5–L7. (15) Kim, D. J.; Kim, D. L.; Rim, Y. S.; Kim, C. H.; Jeong, W. H.;

- Lim, H. S.; Kim, H. J. ACS Appl. Mater. Interfaces **2012**, *4*, 4001–4005. (16) Lee, D. H.; Chang, Y. J.; Stickle, W.; Changa, C. H. Electrochem. Solid State Lett. **2007**, *10*, K51–K54.

- (17) Cho, E. N.; Kang, J. H.; Yun, I. Microelectron. Reliab. 2011, 51, 1792-1795.

- (18) Lee, S. Y.; Kim, D. H.; Chong, E.; Jeon, Y. W.; Kim, D. H. Appl. Phys. Lett. **2011**, 98, 122105.

- (19) Kim, S. J.; Lee, S. Y.; Lee, Y. W.; Lee, W. G.; Yoon, K. S.; Kwon, J. Y.; Han, M. K. Jpn. J. Appl. Phys. **2011**, 50, 024104.

- (20) Kwon, D. W.; Kim, J. H.; Chang, J. S.; Kim, S. W.; Kim, W. J. Appl. Phys. Lett. **2011**, 98, 063502.

- (21) Oh, H.; Park, S. H. K.; Hwang, C. S.; Yang, S.; Ryu, M. K. Appl. Phys. Lett. **2011**, 99, 022105.

- (22) Jeong, J. K.; Yang, H. W.; Jeong, J. H.; Mo, Y. G.; Kim, H. D. Appl. Phys. Lett. **2008**, 93, 123508.

- (23) Jeon, S.; Ahn, S.-E.; Song, I.; Kim, C. J.; Chung, U.-I.; Lee, E.; Yoo, I.; Nathan, A.; Lee, S.; Robertson, J.; Kim, K. *Nat. Mater.* **2012**, *11*, 301.

- (24) Lopes, M. E; Gomes, H. L.; Medeiros, M. C. R.; Barquinha, P.; Pereira, L.; Fortunato, E.; Martins, R.; Ferreira, I. *Appl. Phys. Lett.* **2009**, *95*, 063502.

(25) Ghaffarzadeh, K.; Nathan, A.; Robertson, J.; Kim, S.; Jeon, S.; Kim, C.; Chung, U.-I.; Lee, J.-H. *Appl. Phys. Lett.* **2010**, *97*, 11350411–044305.

(26) Shigesato, Y.; Paine, D. C. Appl. Phys. Lett. 1993, 62, 1268–1270.

(27) Kim, H.; Gilmore, C. M. J. Appl. Phys. 1999, 86, 6451-6461.

(28) Tahar, R. B. H.; Ban, T.; Ohya, Y.; Takahashi, Y. J. Appl. Phys. **1998**, 83, 2631–2645.

- (29) Alam, M. J.; Cameron, D. C. *Thin Solid Films* 2002, 420, 76–82.

(30) Ilican, S.; Caglar, M.; Caglar, Y. *Appl. Surf. Sci.* 2010, 256, 7204–7210.

- (31) Kim, J. K.; Kim, J. Y.; Han, S. C.; Kwak, J. S.; Kim, H. K.; Lee, J. M. J. Electrochem. Soc. 2010, 8, D462–D465.

(32) Murali, S. M.; Rajachidambaram, J. S.; Han, S. Y.; Chang, C. H.; Herman, G. S.; Conley, J. F., Jr. *Solid-State Electron.* **2013**, *79*, 248–252. (33) Kim, J. I.; Ji, K. H.; Jung, H. Y.; Park, S. Y.; Choi, R.; Jang, M.; Yang, H.; Kim, D. H.; Bae, J. U.; Kim, C. D.; Jeong, J. K. *Appl. Phys. Lett.* **2011**, 99, 122102.